29 MAY 29

Issue 11/2008 www.edn.com

Supply Chain: Semicentral.com's Richard Tapping Pg 80

Consumer electronics: too daunting for our addled brains? Pg 10

**Design Ideas** Pg 69

Tales from the Cube: Temperature: your worst enemy? Pg 86

EMBEDDED X86:

VOICE OF THE ENGINEER

## KEYSTONE OF YOUR NON-PC DESIGN?

page 38

PROTOCOL-STACK TESTING FOR LTE TECHNOLOGY Page 29

RENEW

your FREE **magazine** subscription

START

a FREE **e-newsletter** subscription

UNRAVELING THE DYNAMIC-RANGE SPECIFICATION IN MODERN SPECTRUM ANALYZERS

Page 49

MULTICORE-PROGRAMMING FRAMEWORKS FOR EMBEDDED-MULTIMEDIA APPLICATIONS

Page 57

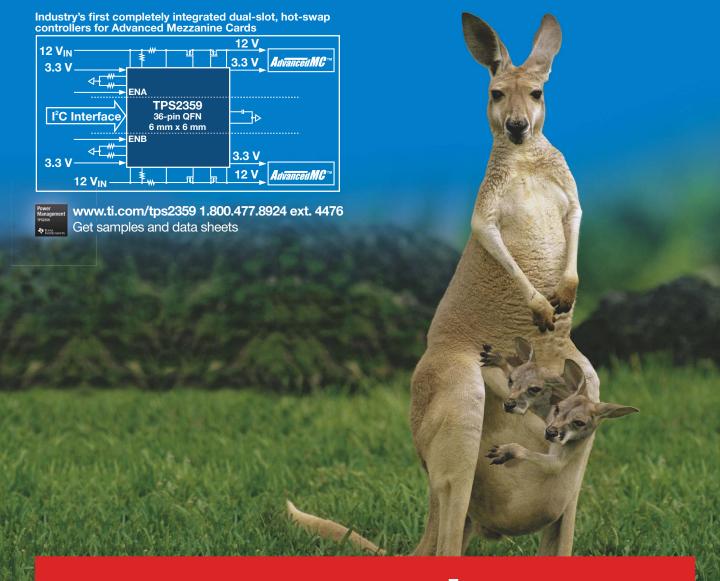

## **Dual-Slot Hot Swap**

### The Naturally Integrated Solution for AdvancedMC<sup>™</sup>

The **TPS2358/9** dual-slot controllers from Texas Instruments manage two 12-V rails and two 3.3-V rails for Advanced Mezzanine Cards in ATCA,  $\mu$ TCA or custom systems. These devices are easy-to-use ATCA/ $\mu$ TCA-compliant solutions with hot swap, ORing and status indicators for all four paths. Optional I²C interface provides programmability and monitoring with the highest integration, flexibility and performance in one small package. **That's High-Performance Analog>>Your Way<sup>TM</sup>**.

Hundreds-of-thousands of parts in stock. Visit www.digikey.com today to see how many!

Quality Electronic Components, Superior Service

Digi-Key Corporation purchases <u>all product</u> directly from its <u>original manufacturer</u>.

www.digikey.com

1.800.344.4539

### **Enter the New World of Bourns**

Automotive Sensors

Circuit Protection Solutions

Magnetic Products

Microelectronic Modules

Panel Controls & Encoders

Precision Potentiometers

Resistive Products

The world of Bourns has grown. An expanding world focused on exceeding our customers' needs. New innovative products and technologies. Expanded application solutions. Plus a worldwide team of technical experts to facilitate the design process and solve tough application problems. All provided to

help customers shorten design cycles

and achieve faster time-to-market.

At Bourns, we have grown to serve you better. Step in – explore the new world of possibilities from Bourns today:

www.bourns.com/newworld

Bourns - the company you have relied on for more than 60 years.

Built on Trust...Based on Innovation

## ZigBee® Made Easy

Z-Accel<sup>™</sup> Simplifies Design, Reduces Time-to-Market

The **CC2480** is the first product from TI's new Z-Accel family of ZigBee-certified network processors which simplifies design and reduces time-to-market. Z-Accel makes it easy to add ZigBee functionality to new or existing products and allows customers the flexibility to work with any MCU for accelerated application development. **That's High-Performance Analog>>Your Way<sup>™</sup>**.

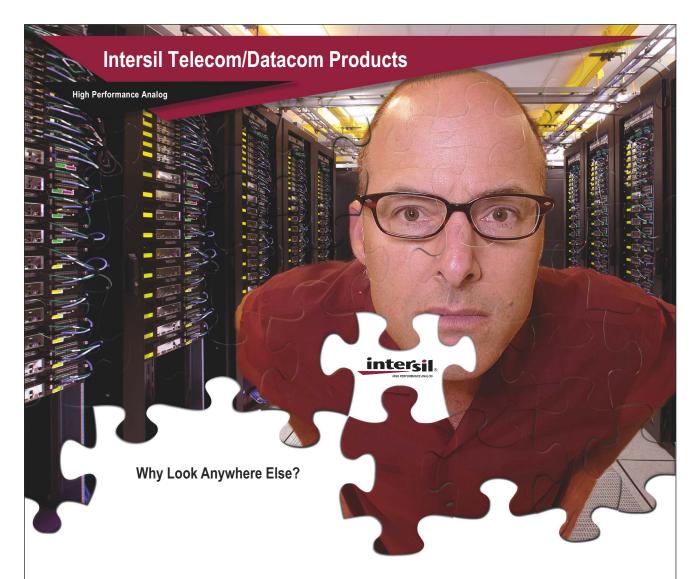

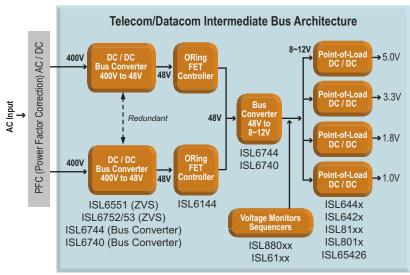

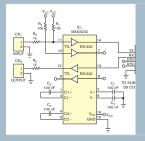

Intersil has your complete Telecom/Datacom solution, from DC/DC Bus Converters to Point-of-Load DC/DC (and everything in between).

Go to www.intersil.com for samples, datasheets and support

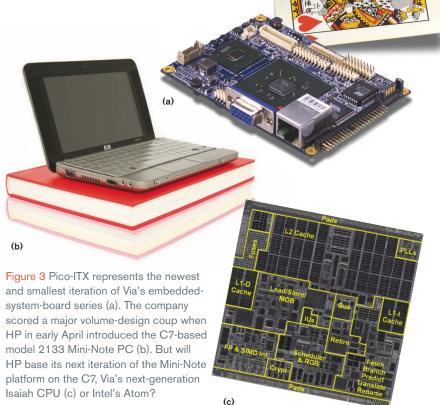

#### Embedded x86: keystone of your non-PC design?

X86 microprocessors may not have the absolute lowest power per megahertz, absolute highest performance per clock tick, or optimum code efficiency when you evaluate them against all possible alternatives. Bundle up the features, though, and the total "kit" often stacks up favorably versus the competition. by Brian Dipert, Senior Technical Editor

#### **Protocol-stack testing** for LTE technology

Effective test strategies can help transform UMTS into a cellular-wideband system.

> by Christina Gessner, Rohde & Schwarz

## EDN contents

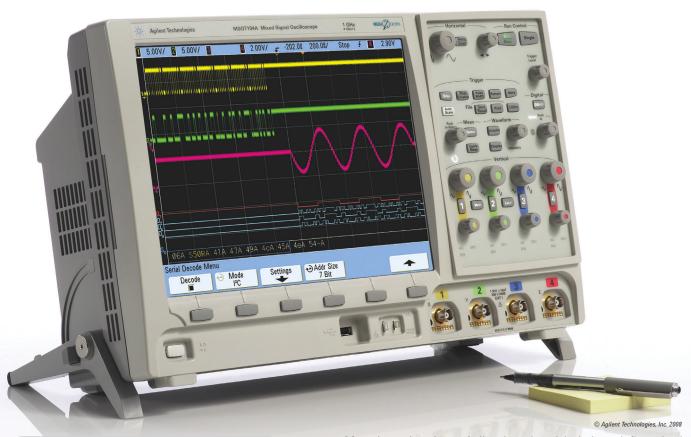

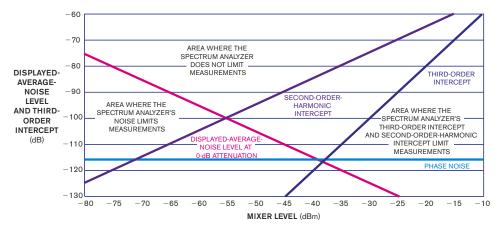

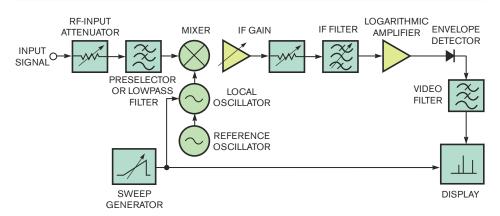

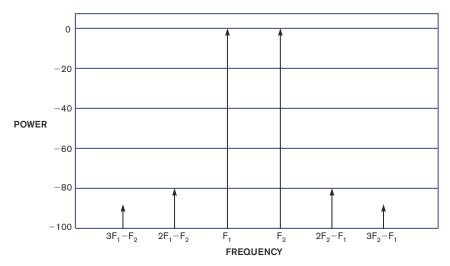

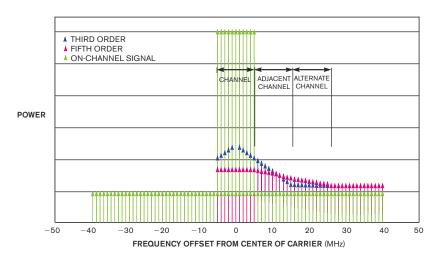

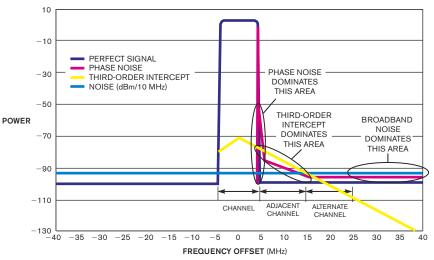

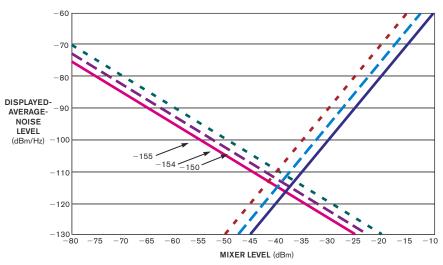

#### Unraveling the dynamic-range specification in modern spectrum analyzers

Using a relatively simple chart to calculate dynamic range, along with speed and accuracy specifications, ensures that you choose the right spectrum analyzer and make appropriate price/performance trade-offs.

> by Satish Dhanasekaran and Darrin Russell, Agilent Technologies

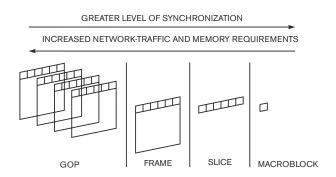

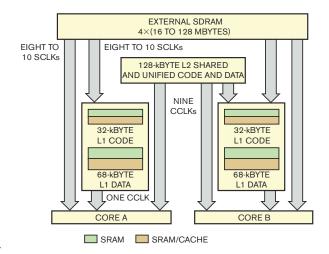

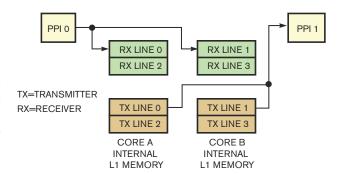

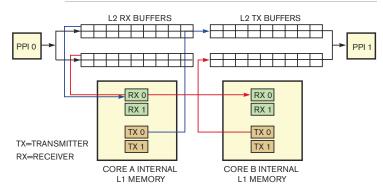

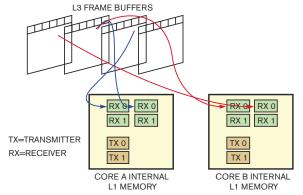

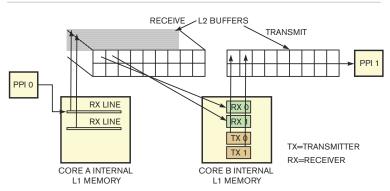

#### Multicore-programming frameworks for embedded-multimedia applications

Understanding the data-access pattern of an application can help you effectively use the memory and system resources of the underlying architecture to develop a scalable parallel application.

by Kaushal Sanghai, Rick Gentile, and David Katz, Analog Devices

## GNIDEAS

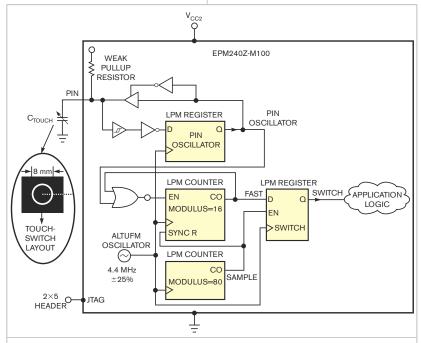

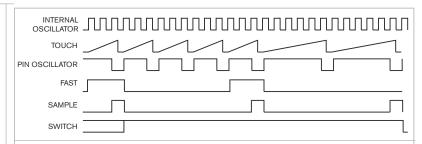

- 69 Capacitive touch switch uses CPLD

- 70 Bit-shifting method performs fast integer multiplying by fractions in C

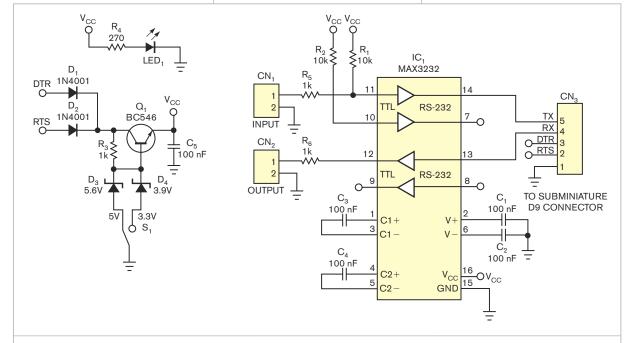

- 72 RS-232-to-TTL converter tests UARTs with a PC

- 74 Hot-swap circuit allows two computers to monitor an RS-232 channel

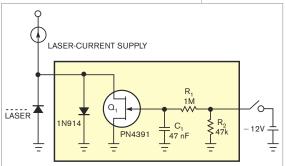

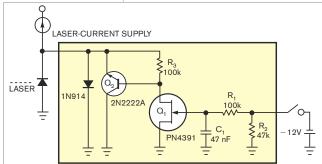

- 76 Improved laser-diode-clamp circuit protects against overvoltages

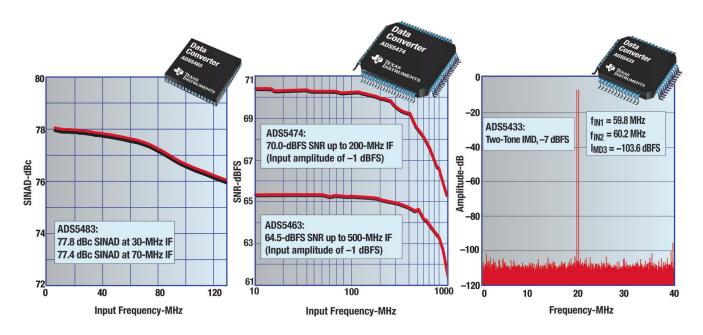

## **Ultimate Performance ADCs**

### **High Speed and Resolution with Buffered Inputs**

High-Performance Analog>>Your Way™

TI's portfolio of small-form factor, high impedance input, bipolar junction transistor ADCs deliver the highest speed, resolution, dynamic performance and widest operational envelope in the industry. Whether you're designing for wideband communications, advanced avionics or test & measurement, TI provides your design with the performance characteristics required to win in the marketplace. **That's High-Performance Analog>> Your Way<sup>TM</sup>.**

| Device  | Description                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS5483 | <b>16-bit, 135-MSPS ADC</b> with high SNR, SFDR and SINAD up to 130-MHz input frequency, with 77.8 SINAD at 30 MHz and 77.4 SINAD at 70 MHz IF. Available in a 9 mm x 9 mm QFN package. Pin-compatible with ADS5482 and ADS5481.                                                           |

| ADS5474 | $ \textbf{14-bit, 400-MSPS ADC} \ \text{provides typical SNR above 70 dBFS and SFDR greater than 80 dBc for input frequencies from DC to 200 MHz.} \\ \text{Available in a 14 mm x 14 mm HTQFP package. Pin-compatible with ADS5463, ADS5444 and ADS5440}. $                               |

| ADS5433 | $ \textbf{14-bit, 80-MSPS ADC} \ \text{ optimized for spurious-free dynamic range with 91-dBc SFDR guaranteed for a 30-MHz input across the I-temp range ($-40^{\circ}$C to 85^{\circ}$C). Available in a 12 mm x 12 mm QFP package. Pin-compatible with ADS5423, ADS5424 and AD6644/45. $ |

| ADS5463 | <b>12-bit, 500-MSPS ADC</b> offers high SNR and linearity with 10 ENOB through second Nyquist. Ideal for wide bandwidth, under sampling applications. Available in a 14 mm x 14 mm HTQFP package. Pin-compatible with ADS5474, ADS5444 and ADS5440.                                        |

www.ti.com/ads5474 1.800.477.8924 ext. 14453

Get samples and evaluation modules

### contents 5.29.08

- 15 Pentek shrinks software-radio module

- 15 NXP opts for soft encryption

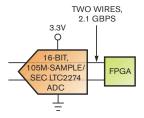

- 16 16-bit, 105M-sample/sec serial-output ADC has two-wire data stream

- 16 IMEMS sensor detects irregularities

- 18 Cougar computer attacks rugged applications

- 18 Microcontroller drains batteries down to 0.9V

- 20 IMEC, Renesas research reconfigurable RF transceivers

- 20 FPGAs target power-constrained designs

- 20 Motor-drive microcontroller has twin inverter outputs

- 22 Research Update: Melting reduces edge roughness, defects in IC features; and more

## DEPARTMENTS & COLUMNS

- 10 **EDN.comment:** Consumer electronics: too daunting for our addled brains?

- 24 Signal Integrity: Pointy tips

- 26 Analog Domain: Honest energy, part two: Readers respond

- 80 Supply Chain: Auction-style site aims to thwart gray market; LED shipments to climb on notebook usage; EPA works with The Green Grid on energy efficiency

- 86 **Tales from the Cube:** Temperature: your worst enemy?

## PRODUCT ROUNDUP

- 82 **Power Sources:** 24V dc/dc converters, power adapters, PCB-mountable ac/dc power supplies, CAN transceivers, switching regulators, and more

- 83 Integrated Circuits: Stereo-audio processors, audio ICs, audio DACs, and more

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc. is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2008 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year, air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6NA. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc., used under license. A Reed Business Information Publication/Volume 53, Number 11 (Printed in USA).

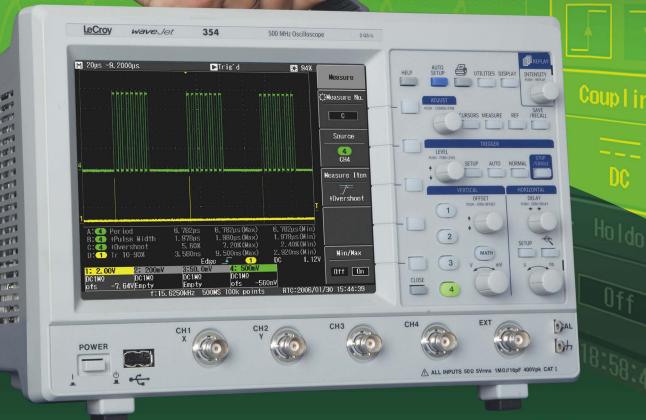

## All the right tools in your hand.

WaveJet® Oscilloscopes

FROM **\$2,950**

### More tools. Better tools. The right tools.

The right tools make debugging faster and easier. The WaveJet 300 Series provides more tools and greater performance than other compact oscilloscopes in the 100 MHz to 500 MHz range.

100m¥

- · Long Memory: 500 k/ch

- Large 7.5" Color Display

- · Compact Size, only 4" Deep

- · USB Connectivity

- · Replay History Mode

- Frequency Counter

## online contents

www.edn.com

HOME

**NEWS CENTER**

**DESIGN CENTERS**

**BUSINESS CENTERS**

PART SEARCH

MORE...

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### The shallow US talent pool

Our talent pool here in the United States is dwindling, putting the United States at extreme risk of losing its standing as a leading nation in terms of technology. Why? And what can be done?

→www.edn.com/080529toc1

#### VUDU: An intriguing (and troubling) embedded-P2P case study

Senior Technical Editor Brian Dipert examines peer-to-peer-incorporating systems with a look at VUDU and its heavy-handed bandwidth transgressions.

→www.edn.com/080529toc2

#### NASA supercomputer to get boost from Intel. SGI

Intel, SGI, and NASA have announced a project that aims to produce a dramatic increase in the space agency's supercomputing capacity.

→www.edn.com/article/CA6558955

#### AMD revamps server road map

Following feedback from OEMs, microprocessor maker Advanced Micro Devices Inc detailed updates to its server road map, addressing platform longevity, performance per watt, and virtualization features. →www.edn.com/article/CA6558966

#### Technology, education driving digital transformation in Middle East

During a speech at the US-Arab Economic Forum, Intel Chairman Craig Barrett discussed the ability of technology to create opportunities for people in the Middle East. →www.edn.com/article/CA6559003

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

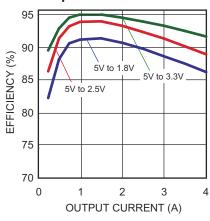

#### **Buck-boost converters change** with the times

Buck-boost converters provide voltages both above and below the input voltage. This feature is useful if your design's input voltage changes drastically or if its load voltage varies.

→ www.edn.com/article/CA6553622

#### Solid-state drives: hard-disk-drive replacements? Huge disappointments? Neither.

While the tit for tat over the relative merits of and prospects for traditional hard-disk drives versus flash-memory-based solidstate drives continues, our expert weighs in with a more pragmatic assessment. Economic and technical factors mean the two storage formats are more likely to coexist and thrive in specific niches.

→www.edn.com/article/CA6556717

#### Circuit and software provide accurate recalibration for baseline PIC microcontroller's internal oscillator

A simple circuit and an assembly-language program allow you to recalibrate the internal oscillator of a PIC microcontroller.

→www.edn.com/article/CA6553623

#### Scrape it: how to probe a microstrip trace with no accessible test points or vias

The lowly scraper is the best tool for the job. Given the right curvature, you can scrape a path just wide enough to reveal a trace under test without exposing other nearby features.

→ www.edn.com/article/CA6553629

Rather than watching the latest YouTube videos, check out some clips that could actually help you in your work.

#### Learn about voltage regulation in automotive electronics

A product engineer from Texas Instruments discusses how to maintain a continuous voltage to critical subsystems during coldcrank, start-stop, load-dump, or weak-carbattery conditions.

→www.edn.com/080529toc3

#### How do I create an FPGA design in 30 minutes?

A representative from Altium demonstrates the creation of a video-capture application using Altium Designer.

→www.edn.com/080529toc4

#### YOUR VIDEO HERE:

#### Upload your clips to EDN:

→www.edn.com/uploadvideo

#### **ENGINEERS' TRUE STORIES**

Tales from the Cube, which appears on the last page of every issue, has become one of EDN's most popular sections because it features true engineering stories as told by EEs. To catch up on any Tales you might have missed-and to learn how to submit your own-please check out our new Tales archive page.

→www.edn.com/tales

#### BY RICK NELSON, EDITOR-IN-CHIEF

## Consumer electronics: too daunting for our addled brains?

t's no secret that consumer spending has been driving the economy, and high-tech company Credence Systems has retooled its businesses to focus on consumer electronics (Reference 1). But it's now questionable whether consumers will continue their spending, despite incometax rebates that some of you may have received by now. At bloomberg. com (Reference 2), economist Ken Goldstein said, "Consumers have gone into the bunkers. [They] fear that their budgets are getting squeezed tighter and tighter. ... A \$600 check isn't enough to turn things around."

But it may be more than a weak economy that drives consumers away from electronic products. They seem not to want much of what they can afford. That's the conclusion I reached after reading an article in The Wall Street Journal that cites a study by Accenture noting that the US electronics industry last year spent about \$13.8 billion handling returned products (Reference 3). The article states, "Especially galling to manufacturers is that many returns are preventable: Only about 5% of returns were because a product was truly defective." Many devices were returned simply because they were too confusing to use.

My conclusion: If you make a product with a user interface so poor that the average consumer can't figure it out, then your product is defective, even if all the transistors, buttons, displays, and other components work.

And if it does turn out that consumers—at least young consumers—aren't smart enough to understand and appreciate the latest high-tech gadgets, the consumer-electronics industry may have only itself to blame. You might infer this conclusion from Mark Bauerlein's new book, *The Dumbest*

# If the average consumer can't figure it out, then your product is defective.

Generation: How the Digital Age Stupefies Young Americans and Jeopardizes Our Future.

The book, slated for a May 15 release, was not available at press time, but in commentary on boston.com, Bauerlein notes that young people don't read books; they spend their time and money on *Grand Theft Auto* instead (**Reference 4**). The predominance of video use, Bauerlein adds, makes schoolwork suffer. Boston.com reinforces this point by citing a *Boston Globe* article noting that "thousands of Massachusetts public school graduates are ending up in remedial reading and writing classes in college."

Bauerlein also says that spelling is a lost art, thanks to instant messaging. And so is composition. He adds, "On MySpace, if you write clearly and compose coherent paragraphs with informed observations on history and

current events, 'buddies' will make fun of you." In short, concludes Bauerlein, "Kids are drowning in teen stuff delivered 24/7 by the tools, and adult realities can't penetrate."

It all has a nice symmetry: The consumer-electronics industry fries our brains, so we are too stupid to be able to set up and operate consumer electronics.

And this situation can have a deleterious effect on the engineering profession. As I've noted before, entry-level engineers are often more adept at playing video games than at working in a real-world laboratory (Reference 5).EDN

#### REFERENCES

- Nelson, Rick, "Credence achieves profitability and will shrink in effort to maintain it," *Test & Measurement World*, Jan 8, 2008, www.tmworld. com/article/CA6518134.

- Chandra, Shobhana, and Alex Tanzi, "Tax Rebates Won't Spark US Economy, Survey Shows," May 9, 2008, www.bloomberg.com/apps/news?pid=20601103&sid=atR6l5T3u.78&refer=us.

- Lawton, Christopher, "The War on Returns," *The Wall Street Journal*, May 8, 2008, pg D1, http://online. wsj.com/article/SB12102082482 0975641.html?mod=technology\_ main\_promo\_left.

- "8 reasons why this is the dumbest generation," boston.com, www. boston.com/lifestyle/gallery/dumbest generation.

- Nelson, Rick, "Talk, no action on education," *Test & Measurement World*, April 2008, pg 7, www. tmworld.com/article/CA6545473.

Contact me at rnelson@reedbusiness.com.

#### MORE AT EDN.COM

+ Go to www.edn.com/080529ed and click on Feedback Loop to post a comment on this column.

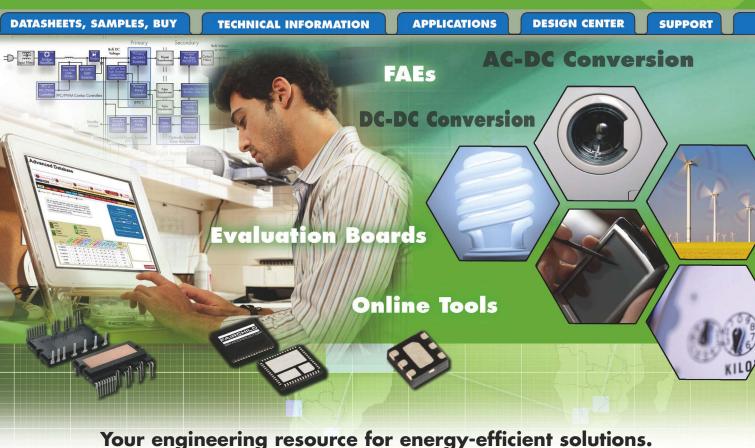

## Save more power. Expend less energy.

#### **Power Factor Correction**

PFC Controllers • PFC/PWM Combo Controllers Low-Side Gate Drivers • MOSFET/IGBT Switches

#### **Isolated DC-DC**

PWM Controllers • MOSFETs

Integrated Power Switches (FPS™) • HVICs

Low-Side/Sync Rectifier Gate Drivers

Optically Isolated Error Amplifiers

Integrated Power Modules (SPM™)

#### **Non-Isolated DC-DC**

Multi-Phase PWM Controllers • MOSFETs Integrated Switching Regulators • DrMOS

Energy conservation is a global concern, and power engineers face increasingly difficult design challenges. That's why Fairchild—The Power Franchise—is committed to providing the industry's most comprehensive portfolio of power components and support services.

From power analog, power discrete, integrated power modules and optoelectronic products to online tools, FAEs and regional centers staffed by experienced power engineers, we have everything you need to minimize energy consumption in power-sensitive applications. Now both your design and your time are energy-efficient.

For more information about Fairchild's energy-efficient solutions, please visit www.fairchildsemi.com/power.

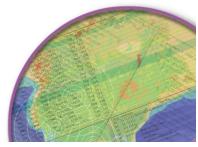

## Intersil's ISL9206 FlexiHash+™ Engine delivers high-security battery authentication at a low cost.

Intersil's ISL9206 is an easy-to-use, robust, and inexpensive battery authentication solution for 1-cell Li-lon/Li-Polymer or 3-cell NiMH series battery packs.

#### ISL9206 Key Features:

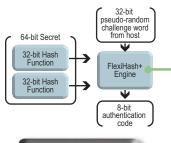

- Challenge/response-based authentication scheme using 32-bit challenge code and 8-bit authentication code.

- FlexiHash+ engine uses two sets of 32-bit secrets for authentication code generation.

- Additional programmable memory for storage.

Patent pending FlexiHash+ engine consists of four separate programmable CRC calculators. Two sets of 32-bit secret codes are used for authentication code generation.

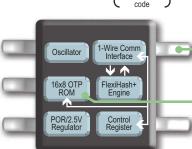

XSD single-wire host bus interface communicates with all 8250-compatible UARTs or a single GPIO pin. Supports CRC on read data and transfer bit-rate up to 23Kbps.

16 bytes of one-time programmable ROM memory for storage of pack information and ID, device authentication secrets, device default settings, and factory-programmed trim parameters.

Go to www.intersil.com for samples, datasheets and support

Intersil – Switching Regulators for precise power delivery.

intersil®

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION

Mark Finkelstein, mark.finkelstein@reedbusiness.com 1-781-734-8431

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-408-345-4437; judy.hayes@reedbusiness.com

#### VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188; kfield@reedbusiness.com

#### EDITOR-IN-CHIEF FDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427: ronald wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com

#### EDITOR-IN-CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-303-265-3017; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

Suzanne Deffree, Managing Editor 1-631-266-3433: sdeffree@reedbusiness.com **POWER SOURCES, ONLINE INITIATIVES**

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### SEMICONDUCTOR MANUFACTURING AND DESIGN

Ann Stefford Mutschler, Senior Editor 1-408-345-4436; ann.mutschler@reedbusiness.com

#### **DESIGN IDEAS EDITOR**

Charles H Small edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439: fax: 1-303-265-3131;

f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523; mbutler@reedbusiness.com

#### **EDITORIAL/WEB PRODUCTION**

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn: Pallab Chatteriee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager

1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015

#### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti yarma@rhi-asia com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.ip Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development,

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect, Intel

#### RON MANCINI Retired Staff Scientist

GABRIEL PATULEA

#### Design Engineer, Cisco

DAVE ROBERTSON

#### Product Line Director, Analog Devices

SCOTT SMYERS

VP Network and System Architecture Division, Sony TOM SZOLYGA

#### Program Manager, Hewlett-Packard

JIM WILLIAMS Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

## **Any Sensor. Any Project.**

NI Data Loggers

#### **NI C Series Data-Logging Family**

- PC-connected or stand-alone deployment

- Expandable I/O from four to 250+ channels

- Rugged devices with long-lasting durability

- Multiple mounting and sensor connectivity options

>> See NI data loggers in action at ni.com/dataloggers

800 327 9894

©2007 National Instruments Corporation. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2007-3329-301-101

PROVEN 2 Y F A R S

When battery failure is not an option...

Remote locations and extreme environments are simply no place for unproven battery manufacturers. When battery failure is not an option, your only option is Tadiran, the only *proven* 20-year battery. So don't take chances, take Tadiran.

2 Seaview Blvd.

Port Washington, NY 11050

1-800-537-1368

(516) 621-4980

Fax: (516) 621-4517

www.tadiranbat.com

### Pentek shrinks software-radio module

t the recent Critical Embedded Systems conference in Scottsdale, AZ, Pentek introduced its latest high-performance, high-resolution software-radio module. The Model 7151 PMC (peripheral-component-interconnect-mezzanine card) features four 200-MHz, 16bit ADCs that feed a proprietary FPGA-IP (intellectual-property) core to deliver 256 channels of digital downconversion. With independent frequency tuning for each channel, the Model 7151 can downconvert any signal within any of the four digitized 100-MHz input bands, making it ideal for GSM (global-system-for-mobile)-communication cell-phone monitoring and signalintelligence applications.

The device comes in four banks of 64 digital-downconversion channels; you can configure each bank for a unique outputsignal bandwidth to accommodate applications requiring mixed-signal types or multiple modulation schemes. You can independently source each bank from any one of the four ADCs, which you typically assign to specific antennas. Software drivers are available for the device, which comes ready to use with developed and installed FPGA code. Software and software-support packages are available for the Linux, Windows, and VxWorks operating systems. The Model 7151 PMC-module version is available for \$14,500, with delivery in 10

- to 12 weeks.-by Warren Webb

- ▶Pentek, www.pentek.com.

- **Critical Embedded Systems**, www. critical-embedded-systems.com.

The Model 7151 contains a complete software-radio system on a single PMC module with 256 digital-downconversion channels and four 200-MHz, 16-bit ADCs.

## NXP opts for soft encryption

XP has announced that it will incorporate NTRU's softwarebased encryption in NXP's ARM7 (www.arm.com)-based microcontrollers. The software-based product will allow you to upgrade a microcontroller in an installed application. NXP will supply the NTRU algorithms as security libraries for its microcontrollers, providing standard features, such as encryption, decryption, digital signatures, RNG (random-number gen-

eration), and key negotiation. These features will establish confidentiality, authentication, and integrity in transactions. The available hash algorithms include SHA (secure hashing algorithm) 1, MD5 (message digest 5) and X9.82 RNG, AES (Advanced Encryption Standard), triple-DES (Data Encryption Standard), RSA (Rivest/Shamir/Adleman), DSA (digital-signature algorithm), and Diffie-Hellman. Pricing will be on a royalty

In opting for a software approach for security, an NXP spokesman explains, a key factor was flexibility and the option of upgrading or retrofitting designs with intersystem data security. The approach has a typical flash-code overhead of approximately 12 kbytes, and it will typically employ about 10% of the computing resources of the company's LPC 2400 device. With the software option, you can change algorithms while the system is in use, either as

a result of the compromising of an algorithm or as a matter of routine. You can also manufacture your product anywhere, with no export-license conditions until you load the software onto the system. To configure the security technology, designers license the code directly from NTRU; the technology runs only on NXP's ARM chips.

-by Graham Prophet NXP Semiconductors. www.nxp.com.

>NTRU, www.ntru.com.

### 16-bit, 105M-sample/sec serial-output ADC has two-wire data stream

inear Technology Corp's new, 16-bit, 105M-sample/sec LTC2274 ADC has a two-wire serial interface, which greatly reduces the number of data lines between the ADC and the FPGA. The data interface is a single self-clocking, differential pair communicating at 2.1 Gbps using 8B/10B encoding. The LTC2274 serial output is compatible with many high-speed-FPGA interfaces, including Xilinx's (www.xilinx. com) Rocket IO, Altera's (www. altera.com) Stratix II GX I/O. and Lattice Semiconductor's (www.latticesemi.com) ECP2M

The part is suitable for communications systems, including cellular base stations, WiMax (worldwide interoperability for microwave access), WCDMA (wideband-code-division multiple access), TDSCDMA (time-

The LTC2274 uses a two-wire data interface that uses 30 fewer pins than a parallel-LVDS (low-voltage-differential-signaling) device.

division-synchronous CDMA), and multicarrier GSM (globalsystem-for-mobile) communication. It also finds use in multichannel ADC systems in ATE (automatic-test equipment), medical imaging, and instrumentation. The device comes in a 6×6-mm QFN-40 package, whose size makes the part useful in space-constrained data-acquisition systems.

The LTC2274 provides an internal transparent-dither circuit that improves the ADC's SFDR (spurious-free-dynamicrange) response to beyond 100 dBc for low-level input signals. A user can enable an optional data scrambler to randomize the spectrum of the serial link, reducing interference from the serial-digital outputs. A programmablegain amplifier in the front end allows either a 2.25 or a 1.5V p-p input range. The part outputs data in two's complement or offset-binary formats. The device has separate shutdown pins for the analog and the digital sections to conserve power. An on-chip duty-cyclestabilizer circuit facilitates non-50%-clock-duty cycles.

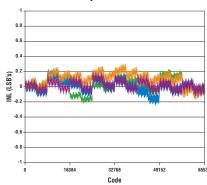

The LTC2274's ac specifications include a 77.5-dBFS (decibels relative to full-scale) SNR (signal-to-noise ratio), a 77.8-dBFS noise floor, and a

RG The device has separate shutdown pins for the analog and the digital sections to conserve power.

100-dB SFDR at baseband. The sample-and-hold section has a 700-MHz full-power bandwidth. The part exhibits 80-fsec-rms jitter, which enables undersampling performance of input frequencies as high as 500 MHz. The LTC2274 consumes 1.3W from a 3.3V analog supply.

The company plans this summer to release pin-compatible 80M- and 65M-sample/sec versions. Linear can screen products to order at sampling rates higher than the rated data-sheet specifications. The LTC2274 sells for \$68 (1000). Production quantities will be available in July in both commercial- and industrial-temperature grades. Demonstration boards and samples are available online now.-by Paul Rako

Linear Technology Corp. www.linear.com/2274.

#### **IMEMS SENSOR DETECTS IRREGULARITIES**

Analog Devices' ADXL001 vibration and shock sensor allows designers of industrial equipment or instrumentation to cost-effectively incorporate continuous, high-performance, high-bandwidth vibration monitoring into their designs. The single-chip, 5×5-mm iMEMS (integrated microelectromechanical-system) package fits into motor-control circuitry or mounts on factory equipment. The chip comes in full-scale dynamic ranges of  $\pm$ 70,  $\pm$ 250, and  $\pm$ 500g, with a 22-kHz resonant frequency, a frequency response down to dc, and nonlinearity of 0.2% of full-scale range.

The chip requires no calibration and works with Analog's SigmaDSP processor and SigmaStudio GUI. It has an extended industrial-temperature range of -40 to +125°C. Input voltage is 3.3 to 5V. The ADXL001 sells for \$35 (1000) and comes in an eight-pin LCC ceramic

-by Margery Conner Analog Devices, www. analog.com.

tion sensor provides early detection of motor-bearing vibration to 22 kHz.

#### **DILBERT By Scott Adams**

2 speed-grade advantage 2X the density 1/2 the power

# SECOND TO NONE

Think AND, not OR. Our new 40-nm Stratix® IV FPGAs give you 2X the density AND a 2 speed-grade advantage AND half the power—with and without 8.5-Gbps transceivers. For production, combine them with our risk-free HardCopy® ASICs for all the benefits of FPGAs AND ASICs. Design with Quartus® II software for the highest logic utilization AND 3X faster compile times. When second is not an option, design with Stratix IV FPGAs.

www.altera.com

## Cougar computer attacks rugged applications

ith an eye toward demanding military, aerospace, medical, and industrial applications, VersaLogic announced the Cougar single-board computer at the April Embedded Systems Conference. The new PC/104-plus board offers designers of ruggedized systems the benefits of fanless operation, soldered-on system memory, and -40 to +85°C extended-temperature operation. The Cougar's AMD (www.amd.com) LX 800 processor delivers Celeron 800-MHz-equivalent performance while drawing less than 5W of power. Standard onboard features include 256 Mbytes of SDRAM, dual 10/100-Mbps

The Cougar PC/104-plus single-board computer features fanless operation, soldered-on system memory, and extended-temperature operation while drawing less than 5W of power.

Ethernet, four USB 2.0 ports, an IDE (integrated-drive-electronics) interface, and three communications ports. A CompactFlash socket provides high-capacity, onboard storage with no moving parts. USB ports provide options for keyboard, mouse, external storage, and other devices.

The board integrates flatpanel support with MMX (multimedia extensions) and 3DNow! extensions for video-intensive applications. The PC/104plus interface supports both ISA (industry-standard-architecture) and PCI (peripheralcomponent-interconnect) addon modules. Standard passthrough connectors allow the board to reside either above or below other PC/104 modules. The Cougar is compatible with a variety of popular operating systems, including Windows, QNX, VxWorks, and Linux. It sells for approximately \$795 (OEM quantities).

-by Warren Webb **VersaLogic Corp**, www. versalogic.com.

#### MICROCONTROLLER DRAINS BATTERIES DOWN TO 0.9V

Silicon Laboratories based its new C8051F9xx line of 8-bit microcontrollers on a new version of the Intel (www.intel.com) 8051 core, which its designers recast as a pipelined, 100-MIPS **CPU.** The company adds mixed-signal and analog features, such as highprecision data converters. The new parts operate at voltages as low as 0.9V to extract the greatest possible life from a single-cell battery. The devices have onboard boost converters that can supply the microcontroller and as much as 65 mW of power for external circuitry, which allows you to use power from a primary cell until the battery drains at 0.9V.

However, Silicon Labs savs that this architecture allows a wide range of efficient battery-operation

modes that go beyond simply draining a single cell to its limits. It operates from 0.9 to 3.6V and incorporates a low-dropout regulator. You can power the device from two cells in series, and the regulator delivers a constant 1.7V to the core. Alternatively, you can use two cells in parallel and exploit the boost converter to operate down to their limits. Either way, the company claims, the configurations to power the chip are more energy-efficient than other devices currently in the market. A graphical/spreadsheet-design tool estimates battery life in the various configurations, taking into account the discharge characteristics of different cell chemistries. As a primary cell drops close to 0.9V,

its remaining capacity is limited, and, at that point, the boost converter makes maximum demands on it, so it may quickly reach its end of life.

In a design with a separate dc/dc converter and microcontroller, the converter must run continuously even if the microcontroller is in sleep mode. In the C8051F9xx, a separate power path allows the converter to be off while the core is in sleep mode, saving power. The C8051F9xx has a typical sleep-mode current of less than 50 nA. The microcontroller can wake up from its low-power sleep mode with the CPU operating at 25 MIPS and can make an analog-to-digital conversion in 2 usec. In active mode, current demand is 170 μA/MHz.

On-chip features include 64 kbytes of flash and 4 kbytes of RAM; a 10-bit, 300k-sample/sec ADC with an internal fast-wakeup-voltage reference; a timing module; and internal oscillators.

Silicon Labs provides an integrated development environment, a target board, cables, and a power supply in a starter kit, or you can begin evaluation using an inexpensive ToolStick daughtercard and base adapter. The chips are in 24-pin,  $4\times4$ mm QFN;  $5\times5$ -mm, 32-pin QFN; and  $7 \times 7$ -mm, 32pin LQFP packages, with prices starting at \$1.99 (10,000). Development kits cost \$99, and ToolStick daughtercards cost \$17.90.-by Graham Prophet Silicon Labs, www.silabs. com.

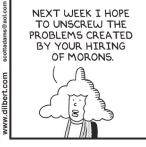

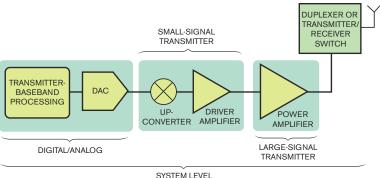

#### Our newest wireless infrastructure innovations

#### **AD6655 IF Diversity Receiver**

Reduces cost of deployment to allow more base stations to improve network quality. 3G support allows increased capability for high data rate applications.

#### AD9230 Single, 12-Bit 250 MSPS ADC

Better base station power efficiency using digital predistortion techniques reduces electricity demand and provides better spectrum purity.

#### AD9788 Dual, 16-Bit 800 MSPS Transmit DAC Simplifies transmit architecture by eliminating mixing stages and provides best ACLR for enhanced network performance.

#### AD8375 and AD8376 Variable Gain Amplifiers

These VGAs enable excellent dynamic range to capture faint transmitted signals in the presence of strong signals.

#### AD9549 and AD9516 Dual Input Network Clock Generator and Distribution Function

Very low noise clock sources ensure best signal quality across multiple wireless platforms.

## Quality connections—in less space, using less power—that's why more base station engineers speak to Analog Devices

As fast as wireless connectivity became pervasive, Analog Devices data converters became the preferred signal processing standard within base station designs. Today, that data conversion technology is just part of a growing family of analog, digital, RF, and mixed-signal solutions for flexible, software-based radio architectures that support wireless standards from GSM to WiMAX. ADI continues to leverage more than 40 years of signal processing innovation to reduce the size, cost, and power demands of base stations, while enabling increased data rates and delivering the calling experience wireless users prefer. And we offer the same application-tuned advantages for medical, industrial, consumer, and automotive designs.

To experience what Analog Devices can do for wireless infrastructure and for other signal processing designs, call 1-800-AnalogD or visit www.analog.com/basestation.

## IMEC, Renesas research reconfigurable RF transceivers

o perform research on 45-nm RF transceivers targeting 1-Gbps cognitive radios, semiconductor supplier Renesas Technology Corp has entered a strategic research collaboration with the IMEC (Interuniversity Microelectronics Center) nanoelectronics and nanotechnology research center's SDR (software-definedradio)-front-end program. This research includes reconfigurable RF products; high-speed, low-power ADCs; and new approaches to digitizing future RF architectures. To bolster development of future mobileelectronics products, Renesas will place researchers onsite at IMEC.

IMEC's SDR-front-end program targets the development of a new generation of cost-, performance-, and powercompetitive reconfigurable radios in 45-nm-digital-CMOS technology, which will contain a programmable center frequency of 100 MHz to 6 GHz and programmable bandwidth of 100 kHz to 40 MHz to cover key communication standards, with a merit comparable to state-of-the-art single-mode transceivers.

The IMEC research program builds on its previous 130-nm RF-transceiver results, including a prototype of a true SDRtransceiver IC. The collaborators will also develop further evolutions of IMEC's ADCs.

"The ability to develop an innovative RF architecture with scaled-down CMOS technology and circuit technologies in transceiver products supporting next-generation cellular standards, such as 3GPP-LTE and 4G, is one of the key differentiators for our products that are superior in cost advantages, performance, and power," says Masao Nakaya, board director and executive general manager of the LSI (large-scaleintegration)-product technology unit at Renesas.

- -by Ann Steffora Mutschler ▶ Renesas, www.renesas.

- Microelectronics Center.

## **⊳Interuniversity** www.imec.be.

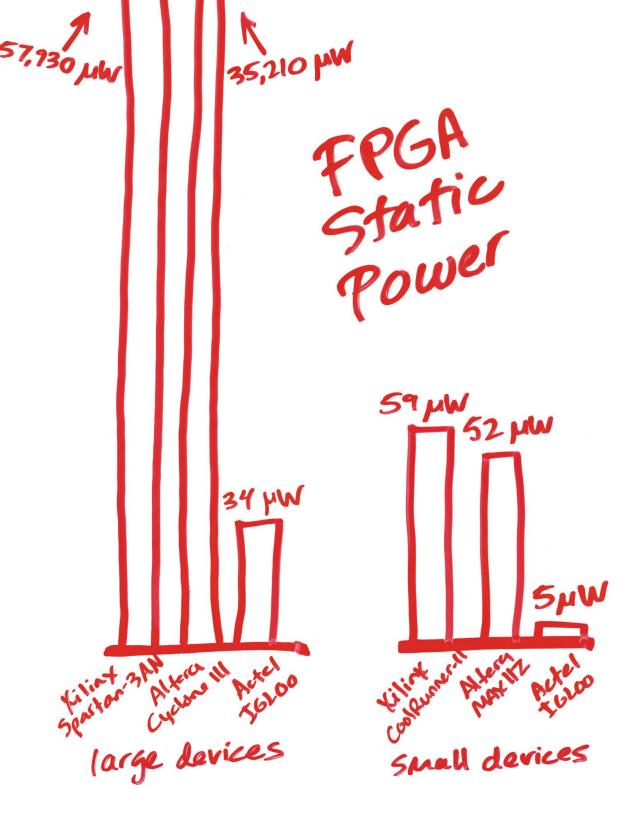

### FPGAs target power-constrained designs

ctel has extended its Igloo series of lowpower FPGAs with Igloo Plus. Whereas the company designed the original devices for maximum density, it optimized the new parts for I/O count. The core-logic structures remain the same as in the earlier parts. The threedevice family spans 30,000 to 125,000 gates with 120, 157, or 212 I/Os. They have as much as 64% more I/Os per equivalent device than the earlier parts, arranged in four banks.

You can hot-swap the connections, which have Schmitttrigger inputs for noise tolerance. As with the Igloo series, they support Actel's Flash Freeze feature, which allows you to place the device in a very-low-power standby mode that nevertheless holds I/O states and from which the device can wake in 1 µsec.

Actel envisages that designers will use the chips for functions such as level shifting, general-purpose-I/O expansion, address- and data-bus multiplexing and decoding, interface translations, and general glue logic. The 30,000-system-gate part has a static power consumption of 5  $\mu$ W. Allowing for the I/O orientation of the Plus series, this consumption is as much as 16 times lower power per I/O than that of some competitive devices, the company asserts. The latest release of Actel's Libero-design package includes a pushbutton poweroptimization option, which you use as a postdesign step to reduce power usage. It will have a minimal effect on performance, impacting speed by a few percentage points

**R** Actel's Flash Freeze feature allows you to place the device in a very-low-power standby mode that nevertheless holds I/O states.

at most. Moreover, the tool gives you feedback on which areas of the design use the most power; a cycle-accurate analysis looks at peak power per cycle as well as average power over the entire simulation. You can also translate this information into a battery-life prediction. Igloo Plus chips will cost slightly less than \$2 to \$4 (250.000).

-by Graham Prophet

▶Actel, www.actel.com.

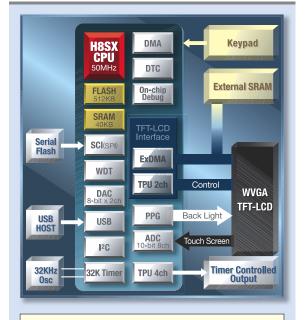

#### MOTOR-DRIVE MICROCONTROL-LER HAS TWIN **INVERTER OUTPUTS**

Renesas designed the SH7137F microcontroller family to meet the needs of designers working on 1- to 100-kW industrial inverters and motor drives. The chip has 256 kbytes of Renesas' MONOS (metal-oxidenitride-oxide-silicon) flash memory onboard. According to Terukazu Watanabe, chief engineer at the company's microcontroller-business unit. MONOS provides high reliability and access time as low as 10 nsec. It allows devices to run directly from flash memory, removing any need for a cache and saving power.

The microcontroller's 12.5-nsec MONOS supports fully deterministic 80-MHz, zero-wait-state operation. It has two timer units and two 12-bit, fast ADCs for measuring the phase currents. It thus provides for three sampleand-hold circuits in each ADC. The conversion time is as fast as 1.25 μsec. For deeply embedded realtime systems, the device has fast, vectored interrupts; Renesas based it on the SH2 core with 16 32-bit-wide general-purpose registers and a MAC (multiply/accumulate unit) for DSP algorithms. The device comes with a suite of peripherals and I/O ports and is available in 80- and 100-pin QFPs.

-by Graham Prophet Renesas, www.renesas. com.

## **Xilinx and Avnet Deliver**

### **Lowest Total Cost... Period.**

With Xilinx® Spartan™-3 Generation FPGAs and Avnet Electronics Marketing's design chain and supply chain support on your side, you're ready to tackle the cost-sensitive high-volume market, where maximum economy and efficiency are required throughout the product lifecycle. With an unprecedented combination of low-cost devices, highly integrated and customizable IP, a variety of time-saving development kits, and a broad array of technical support, services and training, you can save up to 50% in total system cost over competing FPGAs.

Visit www.em.avnet.com/spartan3kits to learn more about Spartan-3 solutions and to purchase a Spartan-3A evaluation kit for only \$39! You too can experience the lowest total cost. Period.

Order Now!

Spartan-3A

Evaluation Kit

\$39 USD

The World's Most Widely Adopted Low-Cost FPGAs

#### M RESEARCH UPDATE

BY RON WILSON

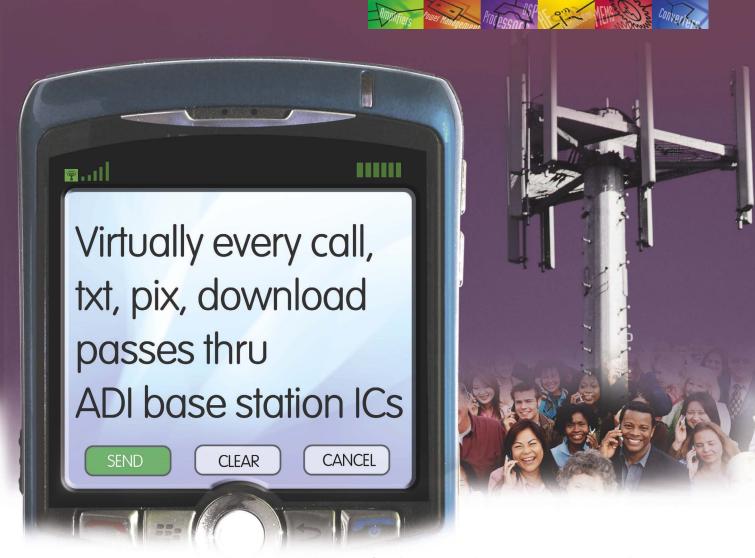

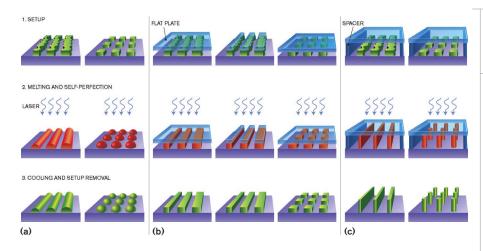

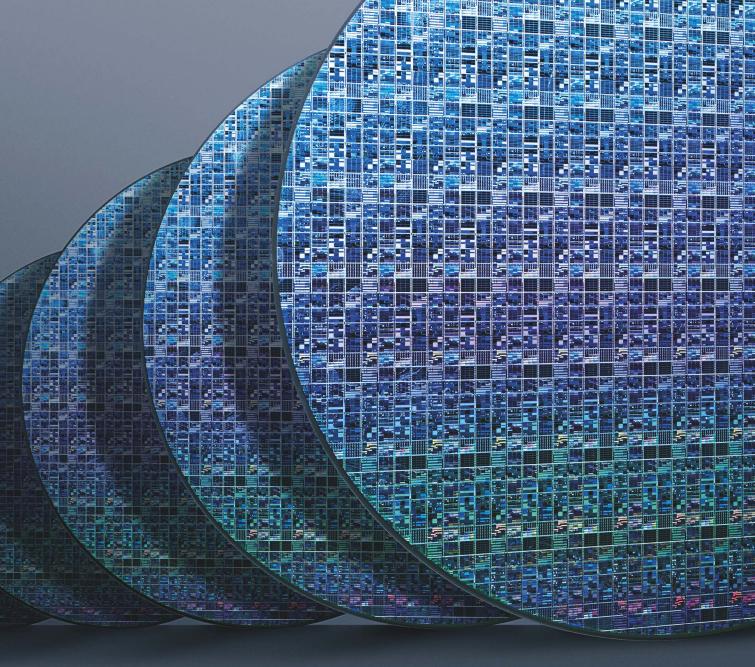

## Melting reduces edge roughness, defects in IC features

project at Princeton University shows that surface heating of small features on an IC can reduce edge roughness and, in some situations, repair defects in metal and semiconductor structures. Project leader Stephen Chou, the Joseph Elgin professor of engineering at the university, used a pulsed excimer laser to melt surface patterns on a test surface without significantly heating the underlying material-vital in IC processes that must adhere to tight thermal budgets or risk damage to underlying structures such as delicate low-kdielectric materials.

Chou heated the features for just long enough to melt them—less than a microsecond. When the laser energy stopped, the structures cooled and reformed under the influence of surface tension. Lines became smoother, irregular polygons became more oval or circular, and so on. Perhaps

more important, Chou found that he could influence the shape of the material as it cooled by applying a thin quartz flat on the surface of the features. This technique led to flat tops and vertical walls on the resolidified features. In measurements on 70-nm-wide chromium lines, this technique reduced an unspecified measure of edge roughness by a factor of five.

In a further experiment, Chou tried positioning the quartz flat slightly above the melted features. He found that, as the features cooled, they tended to stretch up and grow thin-

Researchers used open (a), capped (b), and guided techniques (c) for reducing variations and defects.

ner until the top of the molten liquid touched the plate. The approach resulted in lines that were not only smoother, but also taller and thinner than the original pattern—with obvious implications for increasing control over critical dimensions in some kinds of patterns.

Chou emphasizes that the importance of the technique lies in the fact that, in principle, it allows manufacturers to apply the quartz-plate and laser-pulse process to an entire wafer simultaneously, reducing edge roughness and eliminating small defects for an entire layer of metal or polysilicon features at once. Chou now intends to continue his work by applying the process to 8-in. wafers rather than smaller test areas.

▶ **Princeton University**, www. princeton.edu.

## NOVEL TRANSISTOR ARCHITECTURES BOOST POLYSILICON SUBSTRATES, THICK-OXIDE GATES

Two research projects into novel transistor structures at the Advanced Technology Institute at the University of Surrey have extended the range of processes that might be able to produce high-performance transistors. Both projects focused on producing high switching speeds and high ratios of on-to-off current in transistors fabricated in "disordered" silicon films-presumably including polysilicon and amorphous silicon. The area is important for at least two reasons: High-performance monolithic transistors on a polysilicon film would open the possibility of fast active devices fabricated directly on solar cells or display panels. And it's much easier to deposit, for example, amorphous silicon on a flexible organic substrate than it is to grow a polysilicon or monocrystalline layer on such heat-sensitive materials.

In the first work, the Surrey researchers demonstrated that a transistor fabricated in a disordered film but with a thin channel—on the order of 2 nm thick—could show on-to-off-current ratios on the order of 10<sup>11</sup> and very steep subthreshold slopes. In the second project, researchers demonstrated positive switching characteristics in another new structure, the source-gated transistor. These devices have short source-to-drain separation and relatively thick gate oxide. (See, for example, www.guo.ece.ufl. edu/Report6935/Hong.ppt#262,1,Source-gated Transistor.) Work by Surrey professor John Shannon indicated that such devices—which other researchers are exploring for their ability to deal with short-channel effects as semiconductor scaling reaches extremes—also show promise with amorphous-silicon films.

University of Surrey, Advanced Technology Institute, www.ati.surrey.ac.uk.

## Any Design... Anytime.

## Incredibly Versatile, Incredibly Low Power, 8- and 14-pin PIC<sup>®</sup> Microcontrollers from Microchip.

Microchip's latest low pin count PIC microcontrollers combine the simplicity of an 8-bit architecture with innovative features designed to add intelligence and functionality to a wide variety of applications. Whether you're adding a keypad to a convection oven, an intelligent cooling fan to a power supply, or battery management features to a digital camera, these new PIC microcontrollers can handle the task. With available high-voltage variants and a footprint as small as 4mm x 4mm, this family of low-cost microcontrollers fits easily into any design.

Purchase and program your PIC® microcontrollers and related development tools at...

| Product    | Flash<br>Program Memory<br>Bytes (Words) | RAM<br>Bytes | I/O<br>Pins | 10-bit<br>A/D<br>Channels | Comparators | Timers                   | Packages                      |

|------------|------------------------------------------|--------------|-------------|---------------------------|-------------|--------------------------|-------------------------------|

| PIC12F609* | 1.75K (1K)                               | 64           | 6           | _                         | 1           | 1-16 bit, 1-8 bit, 1-WDT | 8 pin PDIP, SOIC, MSOP, DFN   |

| PIC12F615* | 1.75K (1K)                               | 64           | 6           | 4                         | 1           | 1-16 bit, 2-8 bit, 1-WDT | 8 pin PDIP, SOIC, MSOP, DFN   |

| PIC16F610* | 1.75K (1K)                               | 64           | 12          | _                         | 2           | 1-16 bit, 1-8 bit, 1-WDT | 14 pin PDIP, SOIC, TSSOP, QFN |

| PIC16F616* | 3.5K (2K)                                | 128          | 12          | 8                         | 2           | 1-16 bit, 2-8 bit, 1-WDT | 14 pin PDIP, SOIC, TSSOP, QFN |

<sup>\*</sup>High-voltage variants available.

#### Registration is now open!

#### BY HOWARD JOHNSON, PhD

## Pointy tips

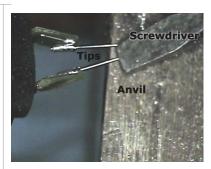

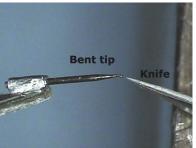

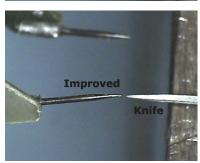

ome high-speed oscilloscope probes come with tips so pointy and sharp that you can set them down onto a PCB (printed-circuit-board) trace just as gently as a phonograph needle and still pick up a great signal. The sharper the point, the less pressure you need to penetrate the thin oxide layer that coats every copper or solder surface.

I recently obtained a set of such probes. After a while, I noticed the probes working less and less well. They seemed to take increasing amounts of pressure to maintain contact. Soon, I found myself attaching weights to the probes or aggressively taping them to maintain that vital contact pressure. I assumed that the probe tips had just become dull.

To check that assumption, I put the tips under a powerful inspection microscope and saw, to my great amusement, that the tips were not at all dull but simply bent like little elf shoes at the tips. My probes were bent so badly that I was touching the trace with what amounts to the side of the probe tip instead of its end.

Now, I check my probes frequently. To do that all you need is a  $20 \times$ power lens—or a 10× lens and really good eyes. When I find a tip starting to go, like this one, I get out two things: a tiny anvil and a hardened-steel screwdriver. For the anvil, I use a drill-press vise. That instrument resembles a miniature bench vise. It is rather flat so that it can hold small things under the spinning chuck of a drill press. Pick one up in a pawn shop or flea market. Mine has hardened faces. You are going to be straightening a couple of hardened-steel pins, so you need tough equipment to do the job.

My screwdriver has a high-quality, hardened blade. Many of the pocketsized screwdrivers for computer work My probes were bent so badly that I was touching the trace with what amounts to the side of the probe tip instead of its end.

are too soft for this job. Get a real machinist's quality tool. Mine has a blade width of 0.125 in.

Place the probe tip on the anvil and gently stroke it with the screwdriver blade. Watch carefully as you do this. Keep turning the probe so you can see it from all directions so that you know which way to hold it for the next stroke. Just go for a little adjustment at a time; don't break it. After a few passes, the tip will look much better. Keep working, and you can make it look almost brand-new.

Now that I've learned about probe tips, I'm more careful setting them down. Before I touch a trace, I check

to make sure that I've completely scraped away the solder mask, and I dress the underlying copper with a little #600 sandpaper glued to the end of a stick. That process thins the oxide, so the probe needs less pressure.**EDN**

#### MORE AT EDN.COM

+ Go to www.edn.com/080529hj to post a comment on this column and to see a brief video clip on how to straighten probe tips.

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

#### ANALOG DOMAIN

#### BY JOSHUA ISRAELSOHN, CONTRIBUTING TECHNICAL EDITOR

## Honest energy, part two: Readers respond

eader response to the last installment of Analog Domain (Reference 1) has been both strong and informative—so much so that I'd like to share some of the feedback with you. One reader asks whether home and business owners can borrow compensation schemes that industrial sites exploit, specifically, compensation capacitors for inductive loads. This kind of apparatus works well in industrial applications because

the loads are essentially large, fixed, and predictable. Still, the industrial-plant operator must bear the cost of the switching apparatus and of the capacitor bank to abide by standard terms that utilities impose on such customers.

Home and nonindustrial business owners rarely present large inductive loads to the grid. The primary inductive loads in typical households include subhorsepower fuel and circulating pumps for heating systems; compressor motors for refrigerators; and drive motors for dishwashers, washing machines, and clothes driers. All of these comparatively modest loads exhibit small duty cycles, which reduces the benefit of com-

pensating them with expensive apparatus.

Nonetheless, millions of these appliances exist, and the aggregate load is hardly negligible. An economic-compensation scheme that some modern motion- Figure 1 The grid-load, control ICs provide is elec- S, is the vector sum of tronic PFC (power-factor real, reactive, and harcorrection) as part of their monic power terms, P, front-end power-manage- Q, and D, respectively. ment capability. These de-

vices are finding their ways into some of the most energy-efficient air conditioners, washing machines, and other home appliances on the market.

Another reader correctly points out that I had neglected to mention harmonic distortion in load currents—a term modern grid-current measurements include. In this more complete model, the grid-load vector, S, is the sum of three other terms: the real power, P; the reactive power, Q; and the distortion factor, D (Figure 1). The D vector does not lie parallel to either axis because a time-domain transform of the frequency-domain data reveals both in-phase and quadrature components with respect to the real power vector.

> Though a negligible concern decades ago, the harmonic content of mainsload current has grown due to the growing prevalence of electronic systems and, in particular, switch-mode supplies. The European Union has led the world in establishing limits on the harmonic content of load currents through standards such as EN 61000-3-2,

which defines four load-device classes and the limits on their load-current spectra extending to the 39th harmonic. The influence of this standard extends beyond Europe: OEMs find it economic to ship standards-compliant products worldwide rather than maintain different designs and inventory for different geographic regions.

A third reader suggests that I had not made sufficiently clear in text what the table revealed: Though a typical CFL's (compact fluorescent lamp's) power factor is a disappointing 0.56, on a per-lumen basis, the lamp still improves on a tungsten-filament bulb's grid use by slightly more than a factor of two. Some electronic ballast chips for office-type fluorescent fixtures include PFC, but I've not vet seen the function in CFLs. Let me know whether you do.

This same reader notes a California Energy Commission report that EPRI Solutions and the Lawrence Berkeley National Laboratory prepared (Reference 2). I found good introductions to EN 61000-3-2 and -4-13 available from Reo UK Ltd (references 3 and 4).EDN

#### **ACKNOWLEDGMENTS**

The author thanks readers Jay Salsburg, Mike Patnode, Rich Bingham, M Simon, John Wendler, Tim Hughes, Pen Jennings, and Nick Jancewicz for their feedback and insights. He regrets that space does not allow even brief discussion of all the questions and related topics they raised.

Joshua Israelsohn is a co-founder of JAS Technical Media, where he manages technical-communication services. You can find his contact information at www. jas-technicalmedia.com/contact.

## You DESIGN It We BUILD It

Use the Most Comprehensive Power Design Tools Available

#### **Custom Module Design System**

Configure a DC-DC converter from hundreds of existing designs for:

- Environmental grade

- Baseplate style

- Pin options or....

- Specify your custom design and verify its feasibility in real time with our module design simulator

#### **Vicor Computer Assisted Design**

- Configure your design of Vicor's VIPAC and VIPAC Array family

- Specify input voltage, output voltages and power levels, mechanical configurations, thermal and connection options.

#### **Design Configurators**

- Select a DC-DC converter from the broadest array of input voltages, output voltages and power levels

- Configure a DC-DC or AC-DC power supply up to three outputs and 600 watts

Identifies the Vicor product(s) that meet your requirements

**Product**

Selector

DC-DC converters, modular filters and front ends, and a broad range of AC-DC and DC-DC configurable power supplies

#### Vicor Systems Product Online Configurator

- Easy, rapid solutions from Westcor's broad product line of AC-DC supplies

- Configure your specific power supply requirements

- Outputs 1 to 400 V in 0.1 V steps

- Up to 20 isolated outputs per supply

- Get your unique model number online and your prototype order can be shipped in 10 days or less

PowerBench gives you the power to specify your own power design solution.

And verify it in real time. All on line.

It's fast, easy, and cost effective!

Visit the Vicor website at www.vicorpower.com/powerbench

Call Vicor Technical Support at 800-927-9474

vicorpower.com/powerbench

"The communication challenge – greater power protection without sacrificing valuable rack space."

## **Control** the future

## Welcome to a new era of power distribution from E-T-A

A new solution developed to support the growing demand in the communication industry for greater power protection without sacrificing valuable rack space.

Driven by the reality that a standard solution does not exist, E-T-A introduces its new power distribution solution with interchangeable breaker modules allowing you to select the overcurrent protection that your application requires.

With the ability to fit into any 19" or 23" rack, the system achieves the highest Power-to-Volume ratio in the industry to date in a 1U package – with total load distribution up to 640A when populated with E-T-A's 482 overcurrent protection devices.

With E-T-A the future is loud and clear.

EFFECTIVE TEST STRATEGIES CAN HELP TRANSFORM UMTS INTO A CELLULAR-WIDEBAND SYSTEM.

## PROTOCOL-STACK TESTING FOR LTE TECHNOLOGY

BY CHRISTINA GESSNER • ROHDE & SCHWARZ

roducers of mobile phones and mobile infrastructure are working on the next big step in the development of the UMTS (universal mobile-telecommunications system): UMTS LTE (long-term evolution). The new standard will ensure that UMTS remains competitive and give users enhanced mobile-Internet access. The first commercial LTE networks could be in place by 2010, and LTE standardization is progressing as part of

Release 8 from the 3GPP (Third Generation Partnership Project). Manufacturers, therefore, will soon need suitable test capability to verify their LTE products.

LTE networks must provide downlink data rates higher than 100 Mbps and uplink rates higher than 50 Mbps. They must also significantly reduce the latency times for packet transmissions so users won't experience unacceptable delays. To achieve these goals, the 3GPP is defining new air-interface-transmission methods and is revamping the protocol and network architecture of UMTS.

Whereas UMTS used WCDMA (wideband-code-division multiple access) for transmitting signals, the LTE downlink uses OFDMA (orthogonal-frequencydivision multiple access), which is particularly robust when handling the varying propagation conditions in mobile radios. The LTE uplink will employ SC-FDMA (single-carrier frequency-division multiple access), which is a precoded OFDMA.

Another significant feature of LTE is bandwidth as high as 20 MHz. Because the usable bandwidth is scalable, LTE can also operate in the 5-MHz UMTS-frequency bands or in even smaller bands. Developers of LTE base stations and wireless devices must also account for a transmission-time interval of only 1 msec between data packets.

LTE systems can also employ MIMO (multiple-input/multiple-output) antenna systems. In one MIMO technique, multiple antennas can transmit the same data stream to improve data-trans-

mission reliability, resulting in diversity gain. In another, the antennas use spatial multiplexing—simultaneously transmitting different data streams to increase throughput; this method results in multiplexing gain. Spatial multiplexing is necessary to achieve the greaterthan-100-Mbps data rates in the downlink direction.

An LTE base station can have as many as four transmitting antennas, and an LTE wireless device will have as many as four receiving antennas. Initial implementations will probably consist of  $2\times2$ -antenna systems—that is, two on the transmitting end and two on the receiving end.

#### PROTOCOL ARCHITECTURE LTE

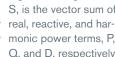

The 3GPP is completely reworking the network and protocol architecture of UMTS so LTE can support high data rates and short latencies. LTE is a purely packet-oriented technology whose developers designed it in accordance with the 3GPP's SAE (system-architecture-evolution) effort. LTE uses a minimal network architecture to reduce latency time (Figure 1). The LTE base station, or eNB (eNodeB), initiates connections on the air interface. It also assigns air-interface resources and performs scheduling.

Each LTE base station connects to the

core network through the 3GPP-defined S1 interface. The base stations themselves interconnect through the X2 interface so they can initiate and complete actions, such as handovers. As a result, the RNC (radio-network controller) that UMTS used is now unnecessary, which significantly reduces the number of internal interfaces in the network. The eNB basically assumes the functions that the RNC previously handled.

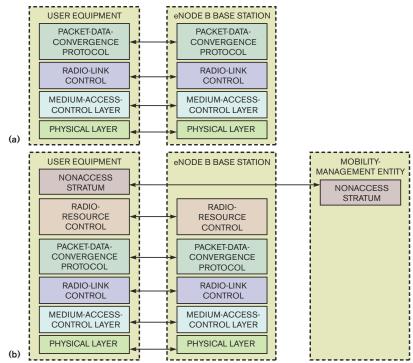

Figure 2 shows the protocol architecture for the user and control planes. The Layer 1 and Layer 2 protocols of the air interface terminate in the wireless device and in the eNB. The Layer 2 protocols include the MAC (medium-access-control) protocol, the RLC (radio-link-control) protocol, and the PDCP (packetdata-convergence protocol). The Layer 3 RRC (radio-resource-control) protocol also terminates in both the wireless device and the base station. The protocols of the NAS (nonaccess stratum) in the control plane terminate in the wireless device and in the mobility-management entity of the core network.

LTE simplifies many of the procedures of UMTS. For example, LTE employs the shared-channel principle, which provides multiple users with dynamic access to the air interface. In contrast to the conventional circuit-switched operation, the packet-oriented LTE network does not assign resources to a user for the entire duration of a connection. Instead, the base station gives the user a resource on the shared channel only when a data packet is ready for transmission. During transmission pauses, LTE can assign the resource to other subscribers. The dedicated channels used in GSM (global-system-for-mobile communication) and UMTS are thus no longer necessary, greatly simplifying the LTE-protocol architecture and ensuring efficient use of the resources on the air interface.

The addition of procedures for link adaptation further improves the performance of the shared channels. With link adaptation, the base station selects the optimum modulation and coding scheme based on the connection quality. The base station also makes frequency-dependent scheduling decisions, such as whether a user would have better connection quality in a specific range of bandwidths. The scheduling

#### AT A GLANCE

- Manufacturers will soon need suitable test capability to verify their LTE (long-term-evolution) products.

- ☑ LTE has bandwidth as high as 20 MHz and can also operate in the 5-MHz UMTS (universal-mobile-telecommunications-system)-frequency bands and even narrower bands.

- During pauses in transmission, LTE can assign the resource to other subscribers, thus obviating the need for dedicated channels, simplifying the architecture, and ensuring efficient use of the resources on the air interface.

- When testing LTE devices, engineers should use a flexible programming language, such as C++, so that they can develop complex test scenarios.

mechanism is therefore complex and, if improperly implanted, can significantly degrade the performance of the LTE system. The stringent timing requirements are important because the base station makes a scheduling decision every millisecond.

LTE differs from UMTS in dispensing with the compressed mode of WCDMA,

which allows a wireless device to take measurements on other frequencies or radio technologies to optimize call quality and to facilitate handovers. For this purpose, data transmission is compressed so that the wireless device can find gaps for performing measurements. This method is relatively complex to implement. Because LTE doesn't use compressed WCDMA, the base station is responsible for providing subscribers with the necessary pauses for these measurements.

An important aspect, particularly from the point of view of network operators, is the integration of LTE into established mobile-radio networks. In addition to GSM/GPRS (general packet-radio service) and the UMTS networks, these include networks employing WiMax (worldwide interoperability for microwave access) and CDMA 2000. To ensure the successful handover of calls from LTE networks to those based on other technologies, the 3GPP specifies suitable handover mechanisms.

#### **PROTOCOL TESTS**

During the early stages of development of LTE-capable chip sets and wireless devices, engineers should perform a

Figure 1 In an LTE network, a base station connects to a core network through the S1 interface. Multiple base stations connect to each other through the X2 interface (not shown).

## Automotive, Industrial, Medical, LCD/Plasma, **Gaming and Printing, Micrel is Everywhere!**

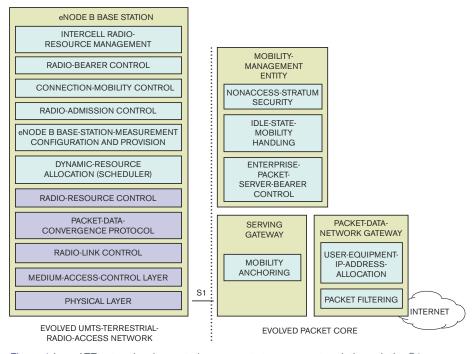

**High-Voltage Synchronous Buck Control IC With Low EMI Option** V<sub>OUT</sub> 3.3V @10A MIC2130/31 Available in 4 x 4 mm MLF® or TSSOP-16

#### **Key Points:**

- 8V to 40V input voltage range

- Low EMI option MIC2131

- Fixed 150/400 KHz

- Adaptive gate drive allows efficiencies over 95%

- Programmable current limit with no sense resistor

- Output over-voltage protection

- Tiny 16-pin 4mm x 4mm MLF® package option

- 16-pin e-TSSOP

- Junction temperature range of -40°C to +125°C

#### **Applications:**

- Automotive Systems

- Industrial/Medical DC-to-DC Point-of-Load

- Gaming Machines

- LCD/Plasma TVs

- **Printer Head Drivers**

- Telecom Systems

or visit Micrel at: www.micrel.com/ad/mic2130.

For more information, contact your local Micrel sales representative Literature 1 (408) 435-2452 Information 1 (408) 944-0800

www.micrel.com

## A midget in size, a giant in performance: MicroSpeed®

Millimeter

### MicroSpeed Power Module: 6–8 amps in only 0.34 ccm.

If there were a type of body power index for connectors, the new MicroSpeed Power Module would eclipse all of its competition. Never before has such a high-performance connector been achieved in such a small space: 6–8 amperes in a construction volume of only 0.34 ccm. Measured at this size, the MicroSpeed surpasses the transmission performance of its ERmet Power Module colleague by a factor of 7.3.

### Continuous mezzanine distances from 5 to 20 mm

4 x 4 male-female combinations deliver 16 mezzanine distances from 5 to 20 mm. The design is configured for automatic assembly, optionally with SMT or THR shield contacts. 3-point contacts with optimized materials guarantee a reliable power supply even under mechanical and thermal loads. This mighty mouse also boasts typical ERNI quality characteristics.

Call ERNI for samples, today.

Figure 2 In the LTE-protocol architecture for the user plane (a) and control plane (b), layer 1 and 2 air-interface protocols terminate in the wireless device and in the eNode B base station. The Layer 2 protocols include the MAC protocol, the RLC protocol, and the PDCP. The Layer 3 RRC protocol also terminates in both the wireless device and the base station. The protocols of the nonaccess stratum in the control plane terminate in the wireless device and in the mobility-management entity of the core network.

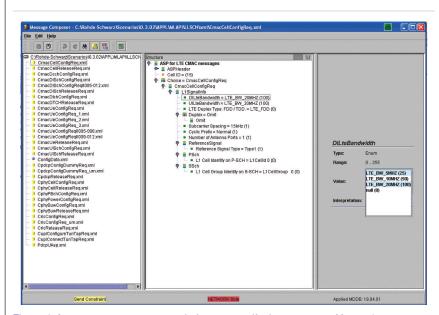

Figure 3 A message composer can help you specify the contents of Layer 3 messages that are used in a test scenario. These messages can perform functions such as setting up a connection.

protocol test and a functional test to ensure that the functioning of the protocols on the air interface complies with the 3GPP LTE specifications. Engineers should also test performance aspects,

such as whether the product can handle the high-data-rate requirements of LTE.

Depending on the degree of integration, you can use various approaches for performing protocol tests. Several test-

## RF testing out of control?

Only Keithley gives you the RF test tools you need to rein in today's devices and tame tomorrow's challenges.

- Test the most complex signal structures, including 802.11n WLAN MIMO and 802.16e Wave 2 WiMAX.

- Configure a 4×4 MIMO test system costeffectively with our newest vector signal generators, vector signal analyzers, and MIMO synchronization unit.

- Generate and analyze signals up to 6GHz repeatably and accurately with our instruments' software-defined radio architecture.

- Reduce your time to market and cost of test with MIMO systems optimized for R&D and production test.

Go to www.keithley.com/tame and try a demo.

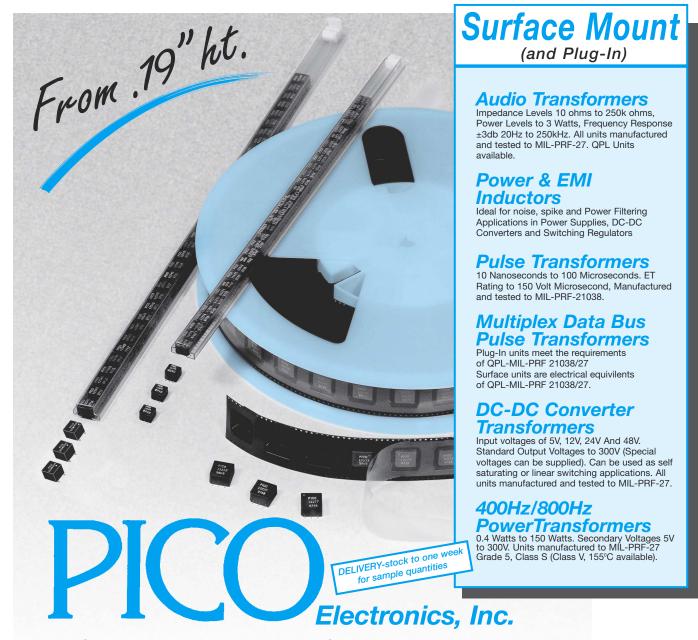

E Mail: info@picoelectronics.com

FAX: 914-738-8225

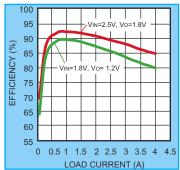

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A Q 🏓 🤨      | E   | m =                       | 7 J           | # # W         |                                           |                                |            |             |                                                                                      |    |                    |